## Common Detector R&D Plan for MeRHIC & MEIC

### First ideas for a detector concept

- □ low mass vertex-tracker / tracker

- important to keep resolution for low energy scattered electrons as good as possible

- Possible solutions

- Gossip (investigated by LHeC)

- GEM-Tracker (STAR)

- high resolution gas-chambers

- TRD

- combine tracking and lepton/hadron separation

- develop a radiator which allows e/h at low momentum p~1GeV (compare Alice-TRD)

- ☐ PID @ mid-rapidity

- > develop a detector concept to separate  $\pi$ , K and p for momenta =< 4 GeV

- Possible solutions

BROOKHAVEN E.C. Aschenauer

- DIRC Panda vs. BABAR concept

- high resolution ToF ~20ns → 4 GeV@1m from IP

- Multi-Gap Resistive Plate Chamber (MRPC)

### Common Detector R&D

#### Photon detection

- > develop cost-effective photon detection replacing PMTs

- Possible Solutions

- big area SiPMs

- work in magnetic field without any shielding

- large dynamic range (number of pixels)

- extremely compact → space → hermitcity

- cost effective → no light guides

- HPDs

### ☐ ION Polarimetry

- $\triangleright$  need small systematics ~3% with high statistics  $\rightarrow$  bunch by bunch measurements

- protons: high intensity polarised jet vs. unpolarised jet

- @ He-3: how? Will the technology for proton work

Prove that a DAQ/trigger system can handle the high event rates and data volumes (a combination of luminosity, detector channels, multiplicity and background) associated with the highest-projected luminosity and, for MEIC, with RF at frequencies of 0.5 (1.5) GHz.

- 1) MEIC/ELIC specific: Push event readout @ relatively small event size

- Explore development of higher channel density per Flash ADCs

- Continue development of on-board high-speed FPGA, including algorithm development, timing simulation, and board layout techniques

- Include latest high-speed Gigabit serial I/O for transporting readout and trigger data. Includes firmware, timing simulation, layout analysis

- R&D for a VXS "switch" path for the event readout data from each crate exceeding present VME readout rate.

- Continue R&D with latest FPGA devices and develop global trigger algorithms for use with pipeline front end modules and large scale, complex detector geometries. E.g., R&D inclusion of vertex tracking in trigger algorithm.

- 2) General (Common R&D): Push data volume rate

BROOKHAVEN E.C. Aschenauer

Develop fast zero subtraction electronics to minimize data volume

Faster ASIC chip development for inner detector readout

The most critical "pre-R&D" is to prove that a DAQ/trigger system can handle the high data rates (a combination of luminosity, detector channels, multiplicate and background) associated with the highest-projected luminosity and RF at frequencies of 0.5 (1.5) GHz. We anticipate this to be a 2-3 year project done in close collaboration between the Fast Electronic Group and the MEIC Nuclear Physicists.

This requires (see slides in Appendix for details):

1) 5.5 FTE-years:

BROOKHAVEN E.C. Aschenauer

one electrical engineer for a three-year period one electrical designer for a three-year period

2) \$150K in procurements

applying 40% of contingency/overhead

Note: in 2007 this task was estimated as 10 FTE-years and \$700K M&S, and was as 5-year task included in plans presented to NSAC/LRP and DOE/NP.

Next-in-line most critical MEIC "pre-R&D" item:

Effort from SC Magnet engineering manpower starting FY10, totaling about 4 FTEs, + small (\$300K?) contracts to verify feasibility of detector and final-focusing SC magnets (following 12 GeV model)

# **BACKUP**

# Appendix: MEIC Physics Most Critical R&D

| Activity          | Detailed Description                                                      | Manpower    |

|-------------------|---------------------------------------------------------------------------|-------------|

|                   |                                                                           |             |

|                   | Explore the development of higher channel density per module. ADC         |             |

|                   | available at higher sampling rates but power consumption is a significant |             |

|                   | challenge. New multichannel, low power devices with serial outputs are    |             |

| Flash ADC         | attractive.                                                               | .5 FTE (EE) |

|                   | Continue development of on board high speed FPGA using the latest         |             |

|                   | FPGA devices. Development includes algorithm development work,            |             |

| FADC FPGA         | timing simulation, and board layout techniques                            | .5 FTE (EE) |

| FADC FPGA         | Continue development with FPGA that contain the latest high speed         |             |

|                   | Gigabit Serial I/O for transporting readout and trigger data.             |             |

|                   | Development includes firmware, timing simulation, and board layout        |             |

| Gigabit FPGA      | analysis tools                                                            | E           |

| Gigabit FPGA      | arialysis tools                                                           | .5 FTE (EE) |

|                   | Build on the existing success of our VXS trigger data transmission. Begin |             |

| Event Readout     | R&D for a VXS 'Switch' path for the event readout data from each crate    |             |

| (DATA Path)       | that easily exceeds the present VME readout data rate.                    | 1 FTE (EE)  |

|                   |                                                                           |             |

| Global Trigger    | Continue R&D with the latest FPGA devices and develop global trigger      |             |

| FPGA              | algorithms for use with pipeline front end modules and large scale,       |             |

| Processing        | complex detector geometries                                               | 1 FTE (EE)  |

| Computer Aided    |                                                                           |             |

| Design Computer   | This is not R&D, but the manpower associated with the R&D efforts will    |             |

| Aided Engineering | require Designers with expertise in high speed, multi-layer circuit       |             |

| CAD/CAE           | boards, schematic capture, and circuit board modeling tools.              | 2 FTE (ED)  |

|                   |                                                                           |             |

| TOTAL (FTE)       |                                                                           | 5.5 FTE     |

BROOKHAVEN E.C. Aschenauer

# Appendix: MEIC Physics Most Critical R&D

| Procurements    |                                                                           | Cost (USD) |

|-----------------|---------------------------------------------------------------------------|------------|

| FPGA Tools      | Xilinx or Altera full development tools (2 Licenses)                      | \$6K       |

| Schematic       |                                                                           | _          |

| capture; Board  |                                                                           |            |

| Layout          | "Altium" design suite or equal (2 Licenses)                               | \$8K       |

| VHDL Synthesis  |                                                                           |            |

| and Simulation  |                                                                           |            |

| Tools           | Aldec, MicroSim, or other tools from FPGA vendors (2 Licenses)            | \$6K       |

| FPGA Evaluation | Latest versions of FPGA devices available from vendors for testing and    |            |

| Modules         | algorithm simulation (2 eval kits)                                        | \$6K       |

|                 | Digital Serial Analyzer (DSA) for high speed multi-Gigabit serial devices | _          |

| Oscilloscope    | and circuit designs                                                       | \$50K      |

| Test crates     | VXS full crate with power supply                                          | \$10K      |

| Peripherals     | Board extenders, fiber optic devices, test equipment, cabling             | \$15K      |

|                 |                                                                           |            |

| TOTAL           |                                                                           | \$101K     |

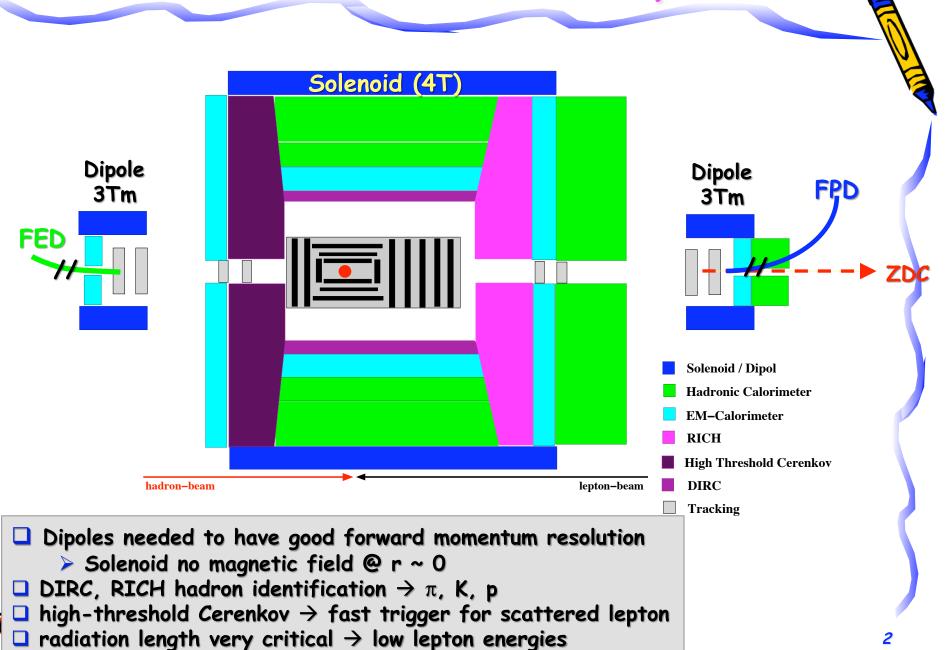

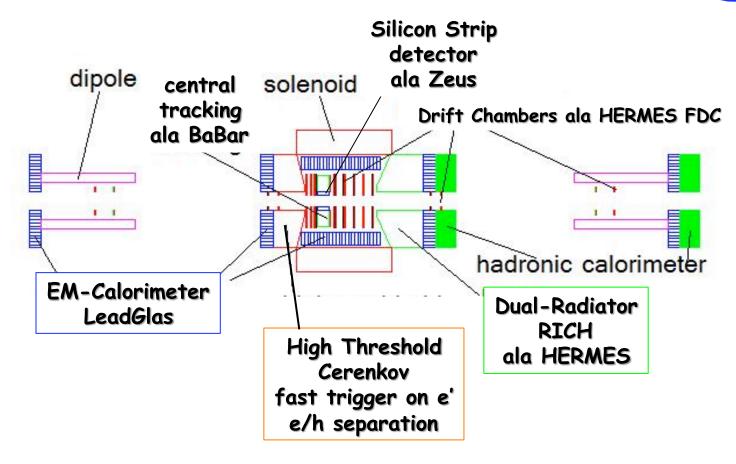

## Detector Requirements from Physics

### ep-physics

- > the same detector needs to cover inclusive (ep -> e'X), semi-inclusive (ep -> e'hadron(s)X) and exclusive (ep -> e'p $\pi$ ) reactions

- large acceptance absolutely crucial (both mid and forward-rapidity)

- particle identification is crucial

- $\blacksquare$  e,  $\pi$ , K, p, n over wide momentum range and scattering angle

- excellent secondary vertex resolution (charm)

- particle detection to very low scattering angle

- around 1° in e and p/A direction

- → in contradiction to strong focusing quads close to IP

- > small systematic uncertainty (~1%/~3%) for e/p polarization measurements

- > very small systematic uncertainty (~1%) for luminosity measurement

#### eA-physics

- > requirements very similar to ep

- challenge to tag the struck nucleus in exclusive and diffractive reactions.

- @ difference in occupancy must be taken into account

### MeRHIC Detector in Geant-3

- □ DIRC: not shown because of cut; modeled following Babar

- □ no hadronic calorimeter in barrel, because of vertical space @ IP-2